Write back cache is a system of data management that dictates cache memory be written back to main memory only when strictly necessary. It allows the CPU faster access to memory like most caches but improves performance significantly compared to methods such as write-through caches.

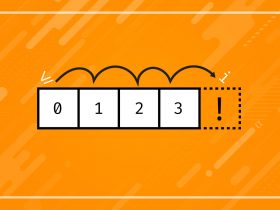

Cache memory is designed to sit between main memory and the CPU to limit the time that certain I/O tasks require. CPU registers are the simplest example and used to greatly increase performance for common data exchanges.

Registers are small in size, however, and many tasks that require larger amounts of memory can see performance boosts from off-CPU cache, often implemented in RAM memory.

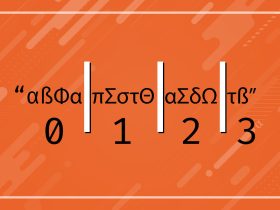

Write-back caches often use what’s called a write-buffer to temporarily hold cache data queued for writing to main memory. This allows the CPU to use only 1 cycle to write to cache, while the write to main memory occurs later.