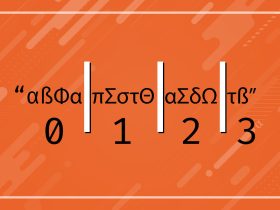

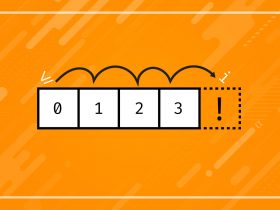

Edge-triggered clocking is a circuit design pattern in which a circuit becomes active at either the negative or positive edge of a clock cycle. This can be described as an on/off triggering and is used to signal state elements to write to internal memory.

Edge-Triggered Clocking is a type of clocking methodology that indicates data in state elements being stable relative to transitions in the clock’s high/low signal.

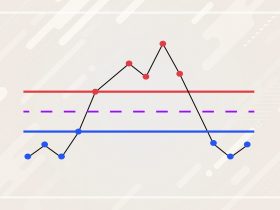

Edge-triggered clocking results in values being either read or written to circuit elements when the clock signal reverses from high to low vice versa. Edge-triggered designs are separated into one of the following two categories:

Positive Edge-Triggered: state elements write values into memory when the clock signal is high.

Negative Edge-Triggered: state elements write values into memory when the clock signal is low.